2/16/2020

Quiz: HW#1 (Submission)

HW#1 (Submission)

This is a preview of the published version of the quiz

Started: Feb 16 at 12:46am

Quiz Instructions

HW#1 was designed for auto-grading so that you may get the feedback i n a more direct way.

Also, it reduces the grading for such a big class size.

I would recommend that you work on the attached HW#1-1.pdf

answers before you are ready to submit your work.

(Also in Canvas) and write down all your

You could have unlimited attempts, but you may not want to key in all the answers again just to fix some of

your answers.

Let me know if you have any more concerns.

Thank you!

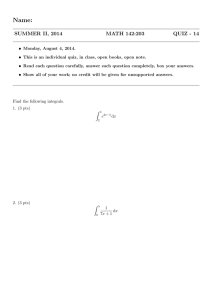

Question 1

3 pts

Match the following decimal numbers to binary using 6-bit 2's complement

representation.

-1610

1310

-310

-1010

2610

-3110

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

1/23

2/16/2020

Quiz: HW#1 (Submission)

-16

[ Choose ]

13

[ Choose ]

-3

[ Choose ]

-10

[ Choose ]

26

[ Choose ]

-31

[ Choose ]

Question 2

3 pts

2.4 [5] <§§2.2, 2.3>

For the MIPS assembly instructions below, what is the corresponding C statement?

Assume that the variables f, g, h, i, and j are assigned to registers $s0, $s1, $s2,

$s3, and $s4, respectively. Assume that the base address of the arrays A and B are in

registers $s6 and $s7, respectively.

Choose the correct C code for the MIPS instructions marked by xxx below

#$s0=f

#$s1=g

#$s2=h

#$s3=i

#$s4=j

#$s6= base address of arrays A

#$s7= base address of arrays B

sll

$t0,

$s0,

2

# xxx

add

$t0,

$s6,

$t0

# xxx

lw

$s0,

4($t0)

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

# xxx

2/23

2/16/2020

Quiz: HW#1 (Submission)

sll

add

lw

$t0,

$s0,

$t0,

2

$s6,

$s0,

[ Choose ]

$t0

4($t0)

[ Choose ]

[ Choose ]

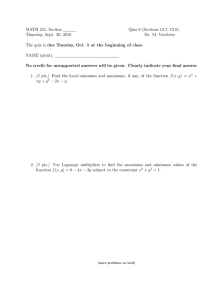

Question 3

5 pts

2.11 For each MIPS instruction, fill in the (decimal) value of the opcode, source register

(rs), extended function code (funct) and target register (rt) fields.

For the I-type instructions, fill in the (decimal) value of the immediate field, and for the Rtype instructions, fill in the (decimal) value of the destination register (rd) field.

Use letters I, R, or J for the type of the instruction format.

Use (decimal) numbers to fill in other answers.

address MIPS code

Type

opcode

rs

80000

addi $t0, $s6, 4

[A1]

[A2]

[A3]

[A4]

[A5] (immediate)

80004

and $t1, $s6, $0

[B1]

[B2]

[B3]

[B4]

[B5]

80008

sw $t2, 4($t1)

[C1]

[C2]

[C3]

[C4]

[C5] (immediate)

80012

lw $s0, 8($s0)

[D1]

[D2]

[D3]

[D4]

[D5] (immediate)

80016

jr

[E1]

[E2]

$a0

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

[E3]

rt

rd

0

0 0

Shmnt funct

0

[B7]

[E7]

3/23

2/16/2020

Quiz: HW#1 (Submission)

A1

[ Choose ]

A2

[ Choose ]

A3

[ Choose ]

A4

[ Choose ]

A5

[ Choose ]

B1

[ Choose ]

B2

[ Choose ]

B3

[ Choose ]

B4

[ Choose ]

B5

[ Choose ]

B7

[ Choose ]

C1

[ Choose ]

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

4/23

2/16/2020

Quiz: HW#1 (Submission)

C2

[ Choose ]

C3

[ Choose ]

C4

[ Choose ]

C5

[ Choose ]

D1

[ Choose ]

D2

[ Choose ]

D3

[ Choose ]

D4

[ Choose ]

D5

[ Choose ]

E1

[ Choose ]

E2

[ Choose ]

E3

[ Choose ]

E7

[ Choose ]

Question 4

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

3 pts

5/23

2/16/2020

Quiz: HW#1 (Submission)

Fill in the Hexadecimal Numbers only.

Loop 80000

80004

80008

80012

opcode

rs

rt

I

5

8

21

Shmnt

funct

add $t1, $t1,

$s6

lw $t0, 0($t1)

bne $t0, $s5,

Exit

(in

Hex)

addi

$s3,$s3,1

j

Loop

J

(in Hex)

Exit:

rd

sll $t1, $s3, 2

80016

80020

Type

(in Hex)

80024

Question 5

3 pts

2.4 [5] <§§2.2, 2.3>

For the MIPS assembly instructions below, what is the corresponding C statement?

Assume that

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

6/23

2/16/2020

Quiz: HW#1 (Submission)

the variables f, g, h, i, and j are assigned to registers $s0, $s1, $s2, $s3, and $s4,

respectively.

the base address of the arrays A and B are in registers $s6 and $s7, respectively.

#$s0=f

#$s1=g

#$s2=h

#$s3=i

#$s4=j

#$s6= base address of arrays A

#$s7= base address of arrays B

sll

$t0,

$s0,

2

sll

add

add

lw

addi

lw

$t1,

$t0,

$t1,

$s0,

$t2,

$t0,

$s1,

$s6,

$s7,

0($t0)

$t0, 4

0($t2)

2

$t0

$t1

add

sw

$t0,

$t0,

$t0,

0($t1)

$s0

B[g] = A[f+1] + A[f] ;

B[g] = A[f+1] + A[g] ;

B[g] = A[g+1] + A[f] ;

B[f] = A[g+1] + A[g] ;

B[f] = A[f+1] + A[g] ;

B[f] = A[g+1] + A[f] ;

None is a correct answer.

Question 6

2 pts

2.7 <§2.3>

Show how the value 0xabcdef12 would be arranged in memory of a little-endian and a

big-endian machine.

Assume the data is stored starting at address 0.

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

7/23

2/16/2020

Quiz: HW#1 (Submission)

Fill in the answers from ab, cd, ef, and 12 only.

Little-Endian

Address

Big-Endian

Data

Address

3

3

2

2

1

1

0

0

Data

Question 7

3 pts

Translate the following MIPS codes to C codes, with the following assumptions.

# f=$s0

#

#

#

#

#

#

g=$s1,

h=$s2

i=$s3

j=$s4

Base address of A = $s6

Base address of B = $s7

sll

add

lw

$t0,

$t0,

$t0,

$s1,

$t0,

0($t0)

2

$s7

addi

sll

$t0,

$t0,

$t0,

$t0,

1

2

addi

lw

$t0,

$s0,

$t0, $s7

0($t0)

# <--- correction here.

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

8/23

2/16/2020

Quiz: HW#1 (Submission)

(Free full credit to everyone.)

f = A[B[g]+1]

f= A[B[g+1] ]

f= A[A[g]+1]

f= B[A[g]+1]

f= B[A[g+1]]

None is a correct answer.

Question 8

5 pts

1.16 <§2.5>

Provide the type and assembly language instruction of instruction described by the

following MIPS fields:

op=0, rs=3, rt=2, rd=3, shamt=0, funct=34

The instruction type is

_______________

The MIPS instruction is

type.

A

$B,

$C,

$D

A = the MIPS instruction corresponding to 0x0

B = destination register

C = first source register

D = second source register

The instruction type is

[ Choose ]

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

9/23

2/16/2020

Quiz: HW#1 (Submission)

A

[ Choose ]

B

[ Choose ]

C

[ Choose ]

D

[ Choose ]

Question 9

3 pts

1.16 <§2.5> )Cont.)

Provide hexadecimal representation of instruction described by the following MIPS fields:

op=0, rs=3, rt=2, rd=3, shamt=0, funct=34

The machine codes in Hex format is ox________________

Note that the answer must contain exactly 8 hexadecimal digits, including the leading

zero digits.

Question 10

5 pts

2.17 [5] <§2.5>

Choose the type and assembly language instruction described by the following MIPS

fields: op=0x23, rs=1, rt=2, const=0x4

Assume assembly language instruction is in the form of A

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

$B, C($D)

10/23

2/16/2020

Quiz: HW#1 (Submission)

The instruction type is

[ Choose ]

A

[ Choose ]

B

[ Choose ]

C

[ Choose ]

D

[ Choose ]

Question 11

3 pts

2.17 [5] <§2.5>

Provide binary representation of instruction described by the following MIPS fields:

op=0x23, rs=1, rt=2, const=0x4

The machine codes in Hex format is ox________________

Note that the answer must contain exactly 8 hexadecimal digits, including any possible

leading zero digits.

Question 12

7 pts

2.18

Assume that we would like to expand the MIPS register file to 128 registers and expand

the instruction set to contain four times as many instructions.

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

11/23

2/16/2020

Quiz: HW#1 (Submission)

2.18.1 [5] <§2.5> How would this affect the size of each of the bit fields in the R-type instructions?

2.18.2 [5] <§2.5> How would this affect the size of each of the bit fields in the I-type instructions?

2.18.3 [5] <§§2.5, 2.10> How could each of the two proposed changes decrease the size of an MIPS

assembly program? On the other hand, how could the proposed change increase the size of an MIPS

assembly program?

The op code will be _______ bits each

for all instructions

[ Choose ]

For I-type instruction, rs and rt fields

would be ____ bits each

[ Choose ]

more registers → more bits per

instruction → could ______ code size

[ Choose ]

more registers → less register spills →

less LW/SW instructions needed →

could _________ code size

more instructions → more appropriate

instruction → could _________ code

size

more instructions → larger opcodes →

could _________ code size

[ Choose ]

[ Choose ]

[ Choose ]

For R-type instruction, rs, rt and rd fields

[ Choose ]

would be ____ bits each

Question 13

3 pts

2.19 Assume the following register contents:

$t0 = 0xAAAAAAAA,

$t1 = 0x12345678

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

12/23

2/16/2020

Quiz: HW#1 (Submission)

2.19.1 [5] <§2.6> What is the value of $t2 for the following sequence of instructions?

Note that the answer has to be exactly 8 hexadecimal digits with upper case letters

only.

li

$t0,

0xAAAAAAAA

li

sll

$t1,

$t2,

0x12345678

$t0,

4

or

$t2,

$t2,

$t1

Question 14

3 pts

2.19.2 [5] <§2.6> (Continue)

What is the value of $t2 for the following sequence of instructions?

Note that the answer has to exactly 8 hexadecimal digits and all the letters have to be

upper-case.

li

$t0,

0xAAAAAAAA

li

sll

$t1,

$t2,

0x12345678

$t0,

4

li

and

$t3,

$t2,

-1

$t2,

$t3

Question 15

3 pts

2.19.3 [5] <§2.6> (Cont.)

What is the value of $t2 for the following sequence of instructions?

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

13/23

2/16/2020

Quiz: HW#1 (Submission)

Note that the answer has to exactly 8 hexadecimal digits and all the letters have to be

upper-case.

li

li

$t0,

$t1,

0xAAAAAAAA

0x12345678

srl

andi

$t2,

$t2,

$t0,

$t2,

3

0xFFEF

Question 16

1 pts

2.21 [5] <§2.6>

Provide a MIPS instruction that may be used to implement the following pseudo

instruction:

not $t1, $t2 # bit-wise invertion

Answer: ____________________ $t1, $t2, $t2

Question 17

1 pts

2.22 [5] <§2.6>

The following C statement and the MIPS assembly instructions perform the identical

operation.

Assume $t1 and $s1 store the base addresses of arrays A and C.

// C code

A[0] = C[0] << 4;

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

14/23

2/16/2020

Quiz: HW#1 (Submission)

#MIPS assembly codes

lw

sll

$t3,

$t1,

0($s1)

$t3,

4

True

False

Question 18

3 pts

2.23 [5] <§2.7> What is the value of $t2 after the following instructions?

The answer has to be a positive decimal number.

ELSE:

li

slt

$t0,

$t2,

0x00101000

$0,

$t0

bne

j

$t2,

DONE

$0,

ELSE

addi

$t2,

$t2,

2

DONE:

Question 19

3 pts

2.26 Consider the following MIPS loop:

li

$t1

10

$s2

$t2,

0

$0,

$t1

beq

subi

$t2,

$t1,

$0,

$t1,

DONE

1

addi

$s2,

$s2,

2

j

LOOP

li

LOOP: slt

DONE:

2.26.1 [5]<§2.7>

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

15/23

2/16/2020

Quiz: HW#1 (Submission)

Assume that the register $t1 is initialized to the value 10 and $s2 is initially zero.

What is the value in register $s2?

Question 20

2 pts

2.26.2 [5] <§2.7> (Cont.)

The following C code is equivalent to the MIPS programs above.

Assume that the registers $s1, $s2, $t1, and $t2 are integers A, B, i, and temp,

respectively.

int

i = 10;

int B = 0 ;

While (i > 0) {

i--;

B += 2;

}

True

False

Question 21

3 pts

2.38 [5] <§2.9> Consider the following code:

li

$t1,

0x10000000

li

lbu

$t2,

$t0,

0x10000010

0($t1)

sw

$t0,

0($t2)

#

# big-endian

Assume that

the register $t1 contains the address 0x1000 0000 and

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

16/23

2/16/2020

Quiz: HW#1 (Submission)

the register $t2 contains the address 0x1000 0010.

the data (in hexadecimal) at address 0x1000 0000 is: 0x11223344.

Note the MIPS architecture utilizes big-endian addressing.

What value is stored at the address pointed to by register $t2?

Answer = 0x ______________________

Note that the answer has to exactly 8 hexadecimal digits, including any possible leading

zeros.

Question 22

2 pts

2.39.m1 [5] <§2.10> Consider the following MIPS assembly code that creates a 32-bit

constant.

What is the value stored at register $t1?

Answer = 0x ____________

Note that the answer has to exactly 8 hexadecimal digits, including any possible leading

zeros.

lui

$t1,

0x2001

ori

$t1, $t1, 0x4924

#lui

#ori

$t1, top_16_bits

$t1, $t1, bottom_16_bi

ts

Question 23

6 pts

2.42 <§§2.6, 2.10>

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

17/23

2/16/2020

Quiz: HW#1 (Submission)

Suppose that the current value of the PC is 0x1FFFF000.

What is the largest (forward) instruction address that a single branch (e.g., BNE or BEQ)

instruction can get to?

Answer = 0x ____________________

What is the smallest (backward) instruction address that a single branch instruction can

get to?

Answer = 0x____________________

Note that the answer has to exactly 8 hexadecimal digits, including any possible leading

zeros.

Letter digits have to be upper case.

Question 24

6 pts

2.40 <§§2.6, 2.10>

Suppose that the current value of the PC is 0x00000000.

What is the largest (forward) instruction address that a single jump instruction can get

to?

Answer = 0x ____________________

What is the smallest (backward) instruction address that a single jump instruction can get

to?

Answer = 0x____________________

Note that the answer has to exactly 8 hexadecimal digits, including any possible leading

zeros.

Letter digits have to be upper case.

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

18/23

2/16/2020

Quiz: HW#1 (Submission)

Question 25

4 pts

2.24 [5] <§2.7>

Suppose the program counter (PC) is set to 0x2000 0000.

Is it possible to use the jump (j) MIPS

assembly instruction to set the PC to

the address as 0x40000000?

[ Choose ]

Is it possible to use the branch-on-equal

[ Choose ]

(beq) MIPS assembly instruction to set

the PC to this same address

(0x40000000)?

Question 26

1 pts

If the current value of the PC is 0x1FFF F000, then we can use a single branch instruction

to get to the PC address at (0x2001 4924).

True

False

Question 27

2 pts

2.10, page 120:

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

19/23

2/16/2020

Quiz: HW#1 (Submission)

What is the MIPS assembly language instruction corresponding to the machine instruction

with the hex value 0x00000000?

j

R-format

addi

sll

mfc0

Undefined opcode: there is no legal instruction that corresponds to 0

Question 28

2 pts

2.10, page 120:

What is the range of addresses for jump and jump and link in MIPS (M =1024K)?

Addresses between 0 and 64M - 1

Addresses between 0 and 256M - 1

Addresses up to about 32M before the branch to about 32M after

Addresses up to about 128M before the branch to about 128M a after

Anywhere within a block of 64M addresses where the PC supplies the upper 6 bits

Anywhere within a block of 256M addresses where the PC supplies the upper 4 bits

Question 29

3 pts

2.6, page 89:

Which operations can isolate a field in a word?

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

20/23

2/16/2020

Quiz: HW#1 (Submission)

AND

A SLL followed by a SRA, and followed by another SLL

A SLL followed by a SRL

A SLLV followed by a SRL, and followed by another SLLV

A SLL followed by a SRL, and followed by another SLL

Question 30

3 pts

2.5, page 87:

What MIPS instruction does this represent? Choose from one of the options below. (Only

one answer)

op

rs

rt

rd

0

8

9

10

sub

$t0,

$t1,

$t2

add

$t2,

$t0,

$t1

sub

$t2,

$t1,

$t0

sub

$t2,

$t0,

$t1

add

$t0,

$t1,

$t2

shamt funct

0

34

None is a correct answer.

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

21/23

2/16/2020

Quiz: HW#1 (Submission)

Question 31

2 pts

2.3, page 72: 2)

Given the importance of registers, what is the rate of increase in the number of registers

in a chip over time?

A) Very fast: They increase as fast as Moore’s law, which predicts doubling the numbe

r of transistors on a chip every 18 months.

B ) Very slow: Since programs are usually distributed in the language of the compute

r, there is inertia in instruction set architecture, and so the number of registers i

ncreases only as fast as new instruction sets become viable.

A) Very fast

B ) Very slow

None is a correct answer.

Question 32

2 pts

2.10, page 120:

What is the range of addresses for conditional branches in MIPS (K =1024)?

Addresses between 0 and 64K - 1

Addresses between 0 and 256K - 1

Addresses up to about 32K before the branch, and up to about 32K after the branch

Addresses up to about 128K before the branch to about 128K after

None is a correct answer.

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

22/23

2/16/2020

Quiz: HW#1 (Submission)

Not saved

https://sjsu.instructure.com/courses/1360616/quizzes/1357459/take?preview=1

Submit Quiz

23/23